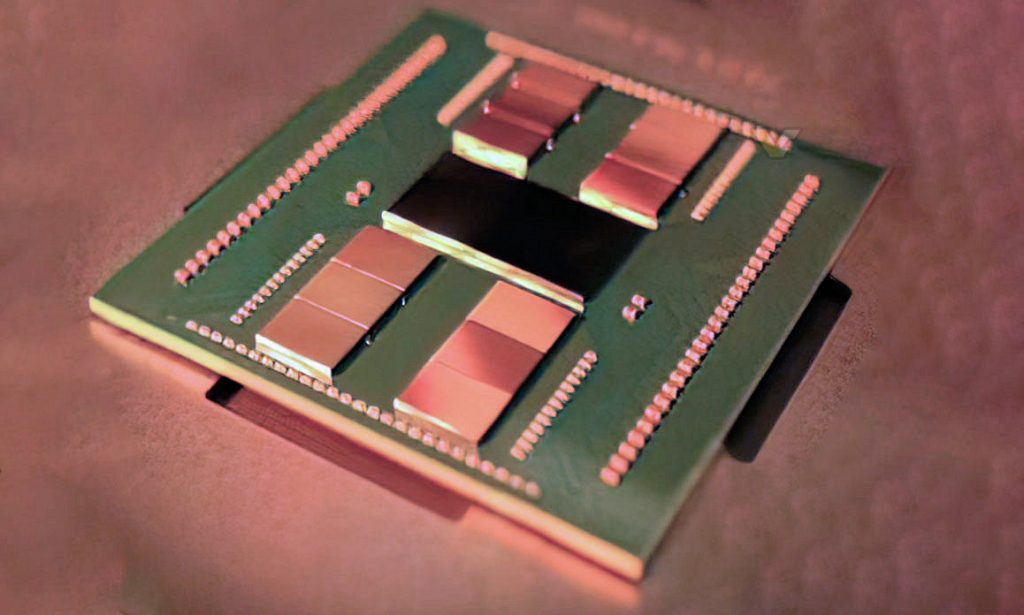

AMD Epyc Genoa mit 12 abgebildeten Chiplets

nur gestern Das erste Bild des neuen SP5-Sockels (LGA6096) ist aufgetaucht und jetzt können wir endlich die nächste Generation des EPYC-Prozessors ohne den eingebauten Heatspreader sehen.

Chiphell-Forumsmitglied „zhangzhonghao“ scheint die erste Person zu sein, die das wahre Bild des kommenden Zen4-Serverprozessors mit dem Codenamen Genoa offenbart. Dies ist das erste Bild, das alle 12 auf SP5 installierten Chiplets zeigt.

AMD EPYC „Genoa“ CPU, Quelle: Chiphell

EPYC Genoa verfügt über bis zu 96 Kerne und 192 Serien in seiner vollständigen Zusammensetzung. AMD wird mehrere SKUs mit teilweise kaputten Kernen herausbringen. Nur weil dieser Prozessor 12 Chips hat, bedeutet das nicht, dass er alle 96 Kerne haben wird.

Jeder Zen4-CCD-Die hat eine Fläche von 72 mm², was 8 mm² kleiner ist als bei Zen3 (z. B. der EPYC-Serie „Milan“). Auch der I/O-Die ist mit etwa 397 mm² kleiner als 416 mm² bei Zen3 EPYC-CPUs. AMD hatte jedoch kein Problem damit, 6 Chips auf jeder Seite des I/O-Dies zu installieren, wenn man bedenkt, dass das SP5 (LGA 6096)-Paket 37 % größer ist als das SP3.

AMD 16-Core EPYC Genoa Prozessor, Quelle: VideoCardz

Die neue SP5-Plattform von AMD wird zusätzlich zu einer PCIe-Gen5-Schnittstelle bis zu 12 DDR5-Speicherkanäle unterstützen. AMD Genoa liefert laut AMD bereits an frühe Kunden. Die neue EPYC 7004-Serie ist nun auf dem Weg, bis Ende dieses Jahres auf den Markt zu kommen.

| Spezifikationen der gemunkelten Prozessoren der AMD EPYC-Serie | ||||||

|---|---|---|---|---|---|---|

| Grafikkarten | 7001 „Neapel“ | 7002 „Rom“ | 7003 „Mailand“ 7003 „Mailand-X“ |

7004 „Genua“ | 7004 „Bergamo“ | |

| 7005 „Taurin“ | starten | 2017 | 2019 | 2021 | 2022 | 2022 |

| 2023/2024 | Gebäude | 14 nm Zinn | 7-nm-Zen 2 | 7-nm-Zen 3 | 5 nm Zen4 | 5 nm Zen4c |

| Zain 5 | Stecker | SP3 (LGA4094) | SP3 (LGA4094) | SP3 (LGA4094) | SP5 (LGA-6096) | SP5 (LGA-6096) |

| SP5 (LGA-6096) | Module/Scheiben | 4xCCD | 8xCCD + 1xIOD | 8xCCD + 1xIOD | 12xCCD + 1xIOD | 12xCCD + 1xIOD |

| TBC | ||||||

| Maximale Kerne | Maximale Uhr | TBC | TBC | |||

| TBC | L2-Cache pro Zentrum | 0,5MB | 0,5MB | 0,5MB | 1 MB | TBC |

| TBC | L3-Cache pro CCX | 8 MB | 8 MB | 32 MB / 96 MB | 32MB | |

| TBC | ||||||

| TBC | ||||||

| Speicherkanäle | Speicherunterstützung | PCIe-Lanes | ||||

| TBC | TBC | |||||

Maximale cTDP TBC Quelle: zhangzhonghao @chevel

Über @9550pro

„Webspezialist. Lebenslanger Zombie-Experte. Kaffee-Ninja. Hipster-freundlicher Analyst.“

More Stories

Die nächste 4K-Minidrohne von DJI passt in Ihre Handfläche

Leaks enthüllen den Namen und das Design des angeblichen PS5 Pro-Geräts

Apple führt mit dem neuesten iOS-Update die KI-Objektentfernung in Fotos ein